# FINAL PROGRAM

The premier conference for Electronic Design Technology

www.ICCAD.com

Sponsored by:

In cooperation with:

# Welcome to the 2010 International Conference on Computer-Aided Design (ICCAD)

ICCAD continues to be the premier -- and most selective -- conference devoted to technical innovations in design automation. ICCAD's program of technical papers, tutorials, and keynote highlights the most important current and future research challenges. A day of workshops on hot topics promises non-stop technical excitement. And as always, a large number of side meetings and social events provide plenty of opportunities for networking and meeting colleagues and friends.

This year's ICCAD starts on Monday, November 8 and continues through Wednesday, November 10; you will find up-to-date details on the conference website http://www.iccad.com. This year's CANDE workshop will be held immediately before ICCAD on November 4, only a short hop away in Monterey. ICCAD's workshops will be on Thursday, November 11. Continuing a practice started last year, ICCAD will integrate its tutorials into the technical program Monday through Wednesday. These tutorials, given by world experts, are an excellent opportunity for updating your knowledge in state-of-the-art and emerging areas.

We received 360 worldwide submissions and the technical program committee, after careful deliberation, selected 108 excellent papers for presentation. These papers are split into 40 sessions over the three days of the technical program. In addition, the ICCAD program this year includes eight tutorials, as well as the designer track, all focused on providing additional broad perspectives for our CAD audience.

ICCAD 2010 is privileged to have a keynote address from James Bouwer, from The National Center for Microscopy and Imaging Research (NCMIR) at the University of California, San Diego. James will outline the challenges of imaging in modern biology - a field that shares a number of challenges with IC design, from the design of the detector chips themselves, to the requirements for complex algorithms, huge data sets, and the need for parallel processing. The considerable expertise of the ICCAD community in dealing with problems of scale and technical complexity can be critical to addressing these new challenges successfully, he believes.

I hope you enjoy a week of ICCAD activities!

**Louis Scheffer** General Chair Janelia Farms Research Campus Howard Hughes Medical Institute

# **Table of Contents**

| Welcome Message                    | Inside Front Cove |

|------------------------------------|-------------------|

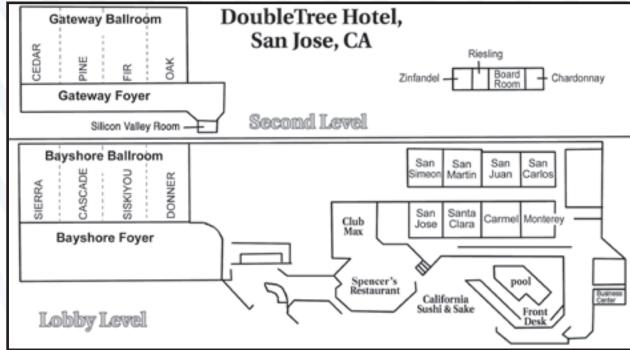

| Hotel Map                          |                   |

| Best Paper Candidates/Committee    |                   |

| CADathlon at ICCAD                 |                   |

| Corporate Sponsors/Technology Fair | 5 - 6             |

| Monday - Wednesday Session Matrix  |                   |

| Opening Session/Awards             |                   |

| Monday Keynote Address             |                   |

| Monday Sessions                    |                   |

| ACM/SIGDA Member Meeting           | 21                |

| Meetings at ICCAD                  |                   |

| Tuesday Sessions                   |                   |

| Tuesday Lunch Talk                 |                   |

| Wednesday Sessions                 |                   |

| Thursday Workshops                 |                   |

| Executive Committee                |                   |

| Program Committee                  |                   |

| Conference Sponsors                |                   |

| General Info/ICCAD Archive         | 52 - 53           |

## **Best Paper Candidates/Award Committee**

## **Best Paper Award Committee**

Karam Chatha Arizona State Univ. Phoenix, AZ

Chris Chu Iowa State Univ. Ames, IA

**Jennifer Dworak** *Brown Univ.* Providence, RI **Puneet Gupta** Univ. of California, Los Angeles San Diego, CA

**Chandramouli Kashyap** *Intel Corp.* Hillsboro, OR

**Xin Li** Carnegie Mellon Univ. Pittsburgh, PA **Sung Kyu Lim** Georgia Institute of Technology Atlanta, GA

**Gi-Joon Nam** IBM Corp. Austin, TX

**Arijit Raychowdhury** Intel Corp. Portland, OR Sherief Reda Brown Univ. Providence, RI

**L. Miguel Silveira** INESC ID/IST - TU Lisbon Lisboa, Portugal

Mircea R. Stan Univ. of Virginia Charlottesville, VA Bill Swartz InternetCAD.com, Inc. Dallas. TX

## IEEE/ACM William J. McCalla ICCAD Best Paper Award Candidates

Monday Sessions

1A.1 FÍDELITY METRICS FOR ESTIMATION MODELS

Haris Javaid, Aleksander Ignjatovic, Sri Parameswaran - Univ. of New

South Wales

2B.1 SETS: STOCHASTIC EXECUTION TIME SCHEDULING FOR MULTICORE SYSTEMS BY JOINT STATE SPACE AND MONTE CARLO

Nabeel Iqbal, Jörg Henkel - Karlsruhe Institute of Technology

3C.1 YIELD ENHANCEMENT FOR 3-D-STACKED MEMORY BY REDUNDANCY SHARING ACROSS DIES

Li Jiang, Rong Ye, Qiang Xu - The Chinese Univ. of Hong Kong

TuesdaySessions

Technology

4B.1 GENERALIZED NONLINEAR TIMING/PHASE MACROMODELING: THEORY, NUMERICAL METHODS AND APPLICATIONS

Chenjie Gu, Jaijeet Roychowdhury - Univ. of California, Berkeley

5A.1 SELECTIVE INSTRUCTION SET MUTING FOR ENERGY-AWARE ADAPTIVE PROCESSORS

Muhammad Shafique, Lars Bauer, Jörg Henkel - Karlsruhe Institute of

7C.1 NATIVE-CONFLICT-AWARE WIRE PERTURBATION FOR DOUBLE PATTERNING TECHNOLOGY

**Szu-Yu Chen**, Yao-Wen Chang - *National Taiwan Univ*.

Wednesday Sessions

8A.1 BI-DECOMPOSITION OF LARGE BOOLEAN FUNCTIONS USING BLOCKING EDGE GRAPHS

Mihir Choudhury, Kartik Mohanram - Rice Univ.

8B.1 OBSTACLE-AVOIDING RECTILINEAR STEINER MINIMUM TREE CONSTRUCTION: AN OPTIMAL APPROACH

Tao Huang, Evangeline F.Y. Young - The Chinese Univ. of Hong Kong

9A.1 SIMPL: AN EFFECTIVE PLACEMENT ALGORITHM

Myung-Chul Kim, Dong-Jin Lee, Igor L. Markov - Univ. of Michigan

9B.1 CHARACTERIZING THE LIFETIME RELIABILITY OF MANYCORE PROCESSORS WITH CORE-LEVEL REDUNDANCY

Lin Huang, Qiang Xu - The Chinese Univ. of Hong Kong

## The CADathlon at ICCAD

## ACM/SIGDA sponsors the ninth annual EDA programming contest at ICCAD

## Sunday, November 7, 7:30am - 5:00pm Donner Ballroom

In the spirit of the long-running ACM programming contest, the CADathlon challenges students in their CAD knowledge, and their problem solving, programming, and teamwork skills. It serves as an innovative initiative to assist in the development of top students in the EDA field. The contest will provide a platform for SIGDA, academia, and industry to focus attention on the best and brightest of next generation CAD professionals.

The students will be given a number of problems that range in difficulty and topics. Information about the CAD areas, relevant papers, and potentially a software framework that will run on Linux will be released one week before the competition. Students will be allowed to work in teams of two. At the contest, students will be given the problem statements and an example test data, but they will not have the judges' test data. Solutions will be judged on correctness and efficiency. The team that passes the most testcases is declared the winner. A handsome prize awaits the winning team. The judges are experts in EDA from both academia and industry.

During the competition students will be presented with six problems in the following areas:

- Circuit Design and Analysis Physical Design

- Logic and High-Level Synthesis

- · System Design and Analysis

- Functional Verification

- · Bio-EDA

The competition is open to all graduate students specializing in CAD currently enrolled full-time in a Ph.D. granting institution in any country. Partial or full travel grants will be provided for qualifying students.

## **CADathlon Organizing Committee:**

Chair, Jarrod Roy, jaroy@us.ibm.com

Vice Chair, Asst. Prof. Sudeep Pasricha, sudeep.pasricha@gmail.com

Vice Chair, Assoc. Prof. Srinivas Katkoori, katkoori@cse.usf.edu

Vice Chair, Sudarshan Banerjee, udarshan\_w@yahoo.com

SIGDA Liaison, Assoc. Prof. R. Iris Bahar

## Sponsored by:

# Corporate Sponsors/Technology Fair

## **Invarian**

5255 Stevens Creek Blvd., Ste. 246 Santa Clara, CA 95051 408-834-5942

www.invarian.com

Invarian develops sign-off analysis solution for analog, digital, and mixed designs from block to SoC level. Synergetic approach to analysis and simulation produces physically correct results that match post-production measurements. Concurrent analysis for power, temperature, timing, and effective voltages in real physical environment helps to get the most complete and accurate analysis data because all analysis engines work in concert and provide feedback to each other. After two years of development, Invarian delivered robust product that helps customers to identify hidden design issues not detectable by any chain of standalone tools. Our solution reduces risk, improves predictability, and lowers respin cost of design process.

## Micro Magic, Inc.

1025 Heatherstone Way, Ste. 101 Sunnyvale, CA 94087 408-414-7647 www.micromagic.com

Micro Magic provides chip design services, specializing in high-speed memories and high-speed datapath designs. Micro Magic provides professional EDA tools for high performance layout and datapath designs.

## National Taiwan University of Science and Technology Department Of Electrical Engineering And Technology

43, Keelung Rd., Section 4

Taipei, 106 Taiwan

http://vlsi.ee.fju.edu.tw/dat/

The DAT (Design Automation and Test) Consortium, funded by the Ministry of Education, Taiwan, is a technology-oriented, inter-collegiate consortium whose mission is to cultivate high-quality human resources in electronic design automation and test in Taiwan. The main tasks of the consortium are to develop teaching/research materials, hold faculty and academia-industry forums, host workshops and student summer camps, promote international collaboration, etc.

# **Corporate Sponsors/Technology Fair**

## Si2 (Silicon Integration Initiative, Inc.)

9111 Jollyville Rd., Ste. 250 Austin, TX 78759 512-342-2244

## www.si2.org

Si2 (Silicon Integration Initiative) is the largest organization of industry-leading semiconductor, systems, EDA and manufacturing companies focused on the development and adoption of standards to improve the way integrated circuits are designed and manufactured, in order to speed time-to market, reduce costs, and meet the challenges of sub-micron design. Now in its 22<sup>nd</sup> year, Si2 is uniquely positioned to enable timely collaboration through dedicated staff and a strong implementation focus driven by its member companies. Si2 represents nearly 100 companies involved in all parts of the silicon supply chain throughout the world. See www.si2.org.

## **Springer**

233 Spring St. New York, NY 10013 212-460-1600 www.springer.com

Springer is one of the world-leaders in Engineering book publishing, boasting a broad range of subject matter, and a history of working with the most prestigious authors in the field. Additionally, Springer publishes a high-value collection of Journals, with a track record of generating the latest, sought after content. Visit our booth to purchase our latest publications at a 20% conference discount. Charles Glaser will be available to answer any questions you may have. Visit springer.com for more information on our latest products.

## Monday, November 8, 2010

Registration - 7:00am - 6:00pm Speaker's Breakfast - 7:30 - 8:30am AV Practice Rooms - 7:00am - 6:00pm

(Gateway Foyer) (Donner/Siskiyou Ballroom) (Chardonnay, Riesling, Zinfandel)

9:00 AM Op

## **Opening Session & Award Presentation**

10:30 AM Keynote Address: Multi-Scale Microscopy of the Nervous System: The Challenge of Imaging and Organizing Data Across Spatial Scales Spanning Twelve Orders of Magnitude - James C. Bouwer, Ph.D., Physicist and Principal Development Engineer, UCSD

(Oak Ballroom)

|                                | Oak Ballroom                                                                                               | Fir Ballroom                                                            | Pine Ballroom                                              | Cedar Ballroom                                                             |

|--------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|

|                                | Tutorial 1                                                                                                 | Session 1A                                                              | Session 1B                                                 | Session 1C                                                                 |

| 11:00 AM<br>— TO —<br>12:30 PM | Designing for Uncertainty:<br>Addressing Process Variations<br>and Aging Issues in Digital<br>Systems      | Fast and Accurate System<br>Estimation, Evaluation, and<br>Optimization | Manufacturing-Aware Design                                 | Analog and Mixed Signal<br>Verification and Optimization                   |

|                                |                                                                                                            | Lunch: 12:30 - 1:30pm (S                                                | iskiyou Ballroom)                                          |                                                                            |

|                                | Tutorial 2                                                                                                 | Session 2A                                                              | Session 2B                                                 | Session 2C                                                                 |

| 2:00 PM<br>— то —<br>4:00 PM   | Reliability Analysis and<br>Optimization at System-Level:<br>A Straddle Between Complexity<br>and Accuracy | Design-Aware Manufacturing                                              | Advances in Embedded Systems<br>and FPGA Synthesis         | Enhancing Test for Delays and<br>Opens Under Power Sensitive<br>Conditions |

|                                |                                                                                                            | Break: 4:00 - 4                                                         | 1:30pm                                                     |                                                                            |

|                                | Tutorial 3                                                                                                 | Session 3A                                                              | Session 3B                                                 | Session 3C                                                                 |

| 4:30 PM<br>6:00 PM             | Analog Challenges in Nanometer<br>CMOS and Digitalization of<br>Analog Functionality                       | Advanced Scheduling for Memory<br>Systems                               | Making Critical Decision on<br>Power in Physical Synthesis | Advances in Yield and Quality<br>Analysis                                  |

|                                |                                                                                                            |                                                                         |                                                            |                                                                            |

Break: 10:30 - 11:00am

ACM/SIGDA Member Meeting: 6:30pm (Donner Ballroom) - Invited Speaker: Scott Kirkpatrick, The Hebrew University of Jerusalem

| Tuesda | v. N | lovem | ber 9 | , 2010 |

|--------|------|-------|-------|--------|

|        |      |       |       | ,      |

Registration - 7:00am - 6:00pm Speaker's Breakfast - 7:30 - 8:30am AV Practice Rooms - 7:00am - 6:00pm (Gateway Foyer) (Donner/Siskiyou Ballroom) (Chardonnay, Riesling, Zinfandel)

| Oak Ballroom Fir Ballroom Pine Ballroom  Tutorial 4 Session 4A Session 4B  8:30 AM System-Level Design - An Design Optimization for Power-             | Cedar Ballroom Session 4C Advances in Global Routing      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 0.20.11                                                                                                                                                |                                                           |

| 8:30 AM System Level Design An D. C. C. C. C. D. C.                                                                | Advances in Global Routina                                |

| 8:30 AM System-Level Design - An Design Optimization for Power- 10:00 AM Industrial Perspective Efficient Synchronous and Asynchronous Systems         | navances in Global nouting                                |

| Break: 10:00 - 10:30am                                                                                                                                 |                                                           |

| Tutorial 4 (cont.) Session 5A Designer Track                                                                                                           | Session 5B                                                |

| 10:30 AM System-Level Design - An Industrial Perspective System-Level Static and Dynamic System-Level Static and Dynamic Sign-Off, Verification, Debug | Leveraging Logics, Wire and 3-D<br>for Physical Synthesis |

| Lunch Presentation 12:00 - 1:15pm (Donner/Siskiyou Ballroom)<br>Semiconductor and EDA Industry - A New Business Model - Lucio Lanza - Lanza TechVentu  | Sponsored By:                                             |

| Tutorial 5 Session 6A Session 6B                                                                                                                       | Session 6C                                                |

| 1:30 PM Beyond-Die Designs: Solutions and Challenges Advances in Biological and Post- CMOS Systems Pushing Clock Distribution Performance              | 3-D-ICs and Detection of Faults<br>and Hardware Trojans   |

| Break: 3:30 - 4:00pm                                                                                                                                   | -1                                                        |

| Tutorial 6 Session 7A Session 7B                                                                                                                       | Session 7C                                                |

| 4:00 PM Organic Electronics Advances in Timing Analysis Parallel Methods for Power Grid and Interconnect Analysis                                      | Physical Design for<br>Manufacturability and Variability  |

| ICCAD Reception: 6:00pm (Gateway Foyer)                                                                                                                | 1                                                         |

|                              |                                                                                                              | Wednesday, Nov                                                                     | ember 10, 2010                                                                  |                                                            |

|------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------|

|                              | Registration - 7:30am - 4:00pm<br>Speaker's Breakfast - 7:30 - 8:30am<br>AV Practice Rooms - 7:00am - 4:00pm | (Gateway Foyer)<br>(Donner/Siskiyou Ballroom)<br>(Chardonnay, Riesling, Zinfandel) |                                                                                 |                                                            |

|                              | Oak Ballroom                                                                                                 | Fir Ballroom                                                                       | Pine Ballroom                                                                   | Cedar Ballroom                                             |

|                              | Tutorial 7                                                                                                   | Session 8A                                                                         | Session 8B                                                                      | Session 8C                                                 |

| 8:30 AN<br>— TO<br>10:00 AM  | Vision for Francis and Discounts                                                                             | Advance in Core Logic Synthesis                                                    | Routing - Theory and Practice                                                   | Power Optimization from System to Circuits                 |

|                              |                                                                                                              | Break: 10:00 - 1                                                                   | 10:30am                                                                         |                                                            |

|                              | Tutorial 7 (cont.)                                                                                           | Session 9A                                                                         | Session 9B                                                                      | Session 9C                                                 |

| 10:30 AN<br>— то<br>12:30 PN | Digital Microfluidic Biochips: A<br>Vision for Functional Diversity<br>and More than Moore                   | Algorithms for Placement: Full<br>House                                            | Analysis and Algorithms for<br>Design and Test in 3-D and Many-<br>Core Systems | Advanced Analysis of Circuit/<br>Device Reliability        |

|                              |                                                                                                              | Lunch: 12:30 - 1:30pm (Donn                                                        | er/Siskiyou Ballroom)                                                           |                                                            |

|                              | Tutorial 8                                                                                                   | Session 10A                                                                        | Session 10B                                                                     | Session 10C                                                |

| 2:00 PM<br>— то —<br>4:00 PN | Manufacturing, CAD and<br>Thermal-Aware Architectures for<br>3-D MPSoCs                                      | Advanced Applications of Logic<br>Synthesis                                        | Advances in Verification                                                        | Recent Advances in Power Grid<br>and Interconnect Analysis |

## Monday, November 8, 2010

## **Opening Session & Keynote Address**

9:00 - 10:30am • Oak Ballroom

## OPENING REMARKS

**Louis Scheffer - General Chair** - Janelia Farms Research Campus Howard Hughes Medical Institute

AWARD PRESENTATIONS

## IEEE/ACM William J. McCalla ICCAD Best Paper Award

This award is given in memory of William J. McCalla for his contributions to ICCAD and his CAD technical work throughout his career.

## SimPL: An Effective Placement Algorithm

Myung-Chul Kim, Dong-Jin Lee and Igor L. Markov - Univ. of Michigan, Ann Arbor, MI

## **IEEE CEDA Early Career Award**

**Luca Daniel** - Massachusetts Institute of Technology, Cambridge, MA For outstanding contributions towards electromagnetic field analysis, parasitic variation-aware extraction and automated parameterized linear and nonlinear stable model reduction.

## 2010 SIGDA Pioneering Achievement Award

**Scott Kirkpatrick** - *The Hebrew Univ. of Jerusalem, Jerusalem, Israel* For his contributions to stochastic optimization, especially simulated annealing, a key element of many modern design automation tool.

## Multi-Scale Microscopy of the Nervous System: The Challenge of Imaging and Organizing Data Across Spatial Scales Spanning Twelve Orders of Magnitude

**James C. Bouwer, Ph.D.,** Physicist and Principal Development Engineer, University of California, San Diego

Experimental advances of the past few decades have given the individual neuroscientist an increasingly powerful arsenal of tools for obtaining new information, extending from molecular structures to the entire nervous system. Scientists have begun the arduous and challenging process of adapting and assembling neuroscience data at all scales of resolution and across disciplines into computerized databases and other easily accessed sources. These multi-scale brain anatomy databases will complement the vast structural and sequence databases created to catalogue, organize and analyze gene sequences and protein products.

A general premise underlying several movements in modern brain research is that with accomplishments like "complete" knowledge of the genomes, solutions of all protein structures, determination of the functioning of key subcellular structures and a map or wiring diagram of the connections of the nervous system - we will next require an information infrastructure that facilitates cooperative assembly of these different forms of data.

## November 7 - 11, 2010 • DoubleTree Hotel • San Jose, CA

# Multi-Scale Microscopy of the Nervous System: The Challenge of Imaging and Organizing Data Across Spatial Scales Spanning Twelve Orders of Magnitude

The ability to explore such a multi-scale composite of knowledge about the brain can be expected to facilitate derivation of new understanding of how the components of the nervous system provide a basis for its complex properties.

Our U.C. San Diego-based group has been leading several interdisciplinary projects central to this grand challenge. While our main goal at the National Center for Microscopy and Imaging Research in San Diego (NCMIR) is to develop advanced technologies which deliver new fundamental understanding of structures on the scale of 1 nm to 100's of  $\mu$ m, a dimensional range that encompasses macromolecular complexes, organelles, and multi-component structures like synapses and key cellular interactions, we have also developed an information infrastructure that is intended to allow these microscopy derived data to be placed in the context of the complex organization of entire nervous systems.

For example, we have developed information systems such as the Whole Brain Catalog and Cell-Centered Database that are tools for mapping molecular and cellular brain anatomy into shared multi-scale mouse brain atlases and databases. To help populate these computerized multi-scale data repositories, our group at NCMIR has developed and disseminated many new molecular labeling methods which allow the same specimens to be examined with both advanced ultra-wide field laser-scanning light microscopy and multi-resolution 3-dimensional electron microscopy methods, like electron tomography. These new labeling and imaging methods are being used to help produce correlated light and electron microscopic data that then flow into the whole brain catalog and its associated databases and neuroscience information frameworks.

Results of research projects where spanning scales has changed previously held views about elements of the nervous system will be presented to illustrate the value of multi-scale anatomical approaches. Examples of how these multi-scale microanatomical frameworks are being used with computer simulations tools to test basic of hypotheses about mechanisms for functioning of the nervous system will also be provided.

In 2000, Dr. Bouwer joined Mark Ellisman's Laboratory, The National Center for Microscopy and Imaging Research (NCMIR). The National Institute of Health (NIH) established National Center for Microscopy and Imaging Research is an internationally acclaimed technology development center and a widely used research resource that develops new technologies and provides researchers with access to many of the most advanced imaging technologies. Dr. Bouwer helped with the launch the development of the NIH Biomedical Informatics Research Network (BIRN) linking major neuroimaging research centers throughout the U.S. BIRN has been a model for multidisciplinary, multi-investigator collaborations and data-sharing.

In 2002, Dr. Bouwer received his Ph.D. in physics from UCSD for his work in Preparation, Theory, and Biological Applications of Highly Luminescent CdSe/ZnS Quantum Dots in Optical and Electron Microscopy. This early work pioneered the use of quantum dots as biological markers for proteins and anti-bodies for both electron and light microscopy. Since then, he has worked as a professional research scientist at UCSD, leading the instrumentation team at the NCMIR under the mentorship of Dr. Mark Ellisman.

11:00am - 12:30pm Pine Ballroom 11:00am - 12:30pm Fir Ballroom

## SESSION 1A • FAST AND ACCURATE SYSTEM **ESTIMATION, EVALUATION, AND OPTIMIZATION**

Sung Kyu Lim - Georgia Institute of Technology Moderators: Hao Yu - Nanyang Technological Univ.

This session starts with two papers on fast and high fidelity estimation and evaluation of system performance for power and performance optimization. The first paper presents several metrics to measure the fidelity of an estimation model that is used in design space exploration of System-on-Chip. The second paper proposes a hybrid system evaluation methodology for fixed-power systems that combines system simulation and analytical models for faster evaluation. This session concludes with a scheduling work that improves performance yield of systems under process variation.

- 1A.1 FIDELITY METRICS FOR ESTIMATION MODELS Haris Javaid, Aleksander Ignjatovic, Sri Parameswaran - Univ. of New South Wales

- 1A.2 FAST PERFORMANCE EVALUATION OF FIXED-POINT SYSTEMS WITH **UN-SMOOTH OPERATORS**

Karthick Parashar, Daniel Menard, Romuald Rocher, Olivier Sentieys, - INRIA

David Novo, Francky Catthoor - IMEC

1A.3 VARIATION-AWARE LAYOUT-DRIVEN SCHEDULING FOR PERFORMANCE YIELD OPTIMIZATION

Deming Chen, Gregory Lucas - Univ. of Illinois at Urbana-Champaign

## SESSION 1B • MANUFACTURING-AWARE DESIGN

Azadeh Davoodi - Univ. of Wisconsin Moderator:

This short session discusses four interesting approaches to bridge the gap between design and manufacturing. The first two papers talk about the timely topic of double patterning lithography (DPL). The first paper discusses implications of DPL on SRAM bitcell design while the second paper proposes wire spreading as an approach to reduce coloring conflicts in DPL. The third paper gives an interesting analysis to show how maximizing information density rather than bit density may be a better SRAM design approach. The final paper of the session extends the Virtual Probe approach for variation characterization to efficiently account for wafer-to-wafer variations.

1B.1 ANALYSIS AND OPTIMIZATION OF SRAM ROBUSTNESS FOR DOUBLE PATTERNING LITHOGRAPHY

> **Vivek Joshi** - Univ. of Michigan Kanak Agarwal - IBM Corp. Dennis Sylvester, David Blaauw - Univ. of Michigan

- 1B.2 WISDOM: WIRE SPREADING ENHANCED DECOMPOSITION OF MASKS IN DOUBLE PATTERNING LITHOGRAPHY Kun Yuan, David Z. Pan - Univ. of Texas, Austin

- MAXIMUM-INFORMATION STORAGE SYSTEM: CONCEPT, 1B.3S IMPLEMENTATION AND APPLICATION Xin Li - Carnegie Mellon Univ.

- MULTI-WAFER VIRTUAL PROBE: MINIMUM-COST VARIATION CHARACTERIZATION BY EXPLORING WAFER-TO-WAFER CORRELATION

Wangyang Zhang - Carnegie Mellon Univ. Xin Li - Carnegie Mellon Univ. Emrah Acar - IBM T.J. Watson Research Ctr.

Frank Liu - IBM Corp.

Rob Rutenbar - Univ. of Illinois at Urbana-Champaign

Cedar Ballroom 11:00am - 12:30pm

# SESSION 1C • ANALOG AND MIXED SIGNAL VERIFICATION AND OPTIMIZATION

L. Miguel Silveira - Cadence Research Labs, INESC-ID/IST - TU Moderator:

Lisbon

The papers in this session provide new ideas for analog and mixed/signal design, analysis and optimization. The first paper addresses the problem of design verification by proposing a semi-formal equivalence checking procedure between behavioral and electrical descriptions. The second paper uses modeling error to improve model fitting and feasibility while meeting constraint targets. The third paper provides a new approach for constructing determinant decision diagrams for symbolic analysis.

1C.1 ON BEHAVIORAL MODEL EQUIVALENCE CHECKING FOR LARGE ANALOG/MIXED SIGNAL SYSTEMS

Amandeep Singh, Peng Li - Texas A&M Univ.

- 1C.2 AN ALGORITHM FOR EXPLOITING MODELING ERROR STATISTICS TO **ENABLE ROBUST ANALOG OPTIMIZATION** Michael Orshansky, Mario Lok, Constantine Caramanis, Ashish Kumar Singh, Kareem Ragab - Univ. of Texas, Austin

- A SIMPLE IMPLEMENTATION OF DETERMINANT DECISION DIAGRAM 1C.3 **Guoyong Shi** - Shanghai Jiao Tong Univ.

11:00am - 12:30pm

Oak Ballroom

## TUTORIAL 1 • DESIGNING FOR UNCERTAINTY: ADDRESSING PROCESS VARIATIONS AND AGING **ISSUES IN DIGITAL SYSTEMS**

Moderator: Diana Marculescu - Carnegie Mellon Univ.

Driven by aggressive technology scaling and sub-wavelength lithography, there has been a marked increase in the variability of process technology parameters. In addition, due to increased power density and stricter thermal envelopes, environmental parameter variability (e.g., temperature and voltage variation) and their impact on system lifetime increase as well.

Regardless of its source or manifestation, such design uncertainty poses a major challenge in designing complex integrated systems due to increased performance variability, and decreased reliability and system lifetime of logic and memory. Variability-aware and system lifetime-aware design methodologies are needed for all levels of abstraction.

Existing approaches target variability at the circuit/gate/layout level and do not provide sufficient leverage since they do not provide capabilities that can be easily used at higher levels of abstraction, where much of the overall optimization can be done more effectively.

This tutorial will give an overview of the most important aspects of variability and aging at physical, environmental, and circuit levels of abstraction. It will also describe system-level design methodologies capable of capturing these effects at the micro-architecture and architecture levels for both performance and power.

## AGING ANALYSIS AT GATE AND MACRO CELL LEVEL

**Ulf Schlichtmann**, Dominik Lorenz, Martin Barke - Technische Univ. München

## RESILIENT MICROPROCESSOR DESIGN FOR IMPROVING PERFORMANCE AND ENERGY EFFICIENCY

Keith A. Bowman, James W. Tschanz - Intel Corp.

## PROCESS VARIATION AWARE PERFORMANCE MODELING AND DYNAMIC POWER MANAGEMENT FOR MULTICORE SYSTEMS Siddharth Garg, Diana Marculescu - Carnegie Mellon Univ.

Sebastian X. Herbert - DC Energy

2:00 - 4:00pm

Fir Ballroom

## SESSION 2A • DESIGN-AWARE MANUFACTURING

Minsik Cho - IBM Corp. Moderator:

This session discusses several new design-aware and process-aware mask methodologies. The first three papers discuss design-aware mask optimization and inspection. Specifically, they propose a mask inspection technique considering design sensitivity, a mask perturbation methodology to improve manufacturability, and a template mask methodology to reduce mask costs. The fourth paper presents a fast layout decomposition technique for double patterning lithography (DPL). The last paper presents a process monitor methodology to reduce back-end manufacturing costs.

### 2A.1 **DESIGN-AWARE MASK INSPECTION**

Abde Ali Kagalwalla, Puneet Gupta - Univ. of California, Los Anaeles Chris Progler, Steve McDonald - Photronics, Inc.

### 2A.2 SMATO: SIMULTANEOUS MASK AND TARGET OPTIMIZATION FOR IMPROVING LITHOGRAPHIC PROCESS WINDOW

Shayak Banerjee - Univ. of Texas, Austin Kanak Agarwal - IBM Corp.

Michael Orshansky - Univ. of Texas, Austin

### 2A.3 TEMPLATE-MASK DESIGN METHODOLOGY FOR DOUBLE PATTERNING TECHNOLOGY

Chin-Hsiung Hsu, Yao-Wen Chang- National Taiwan Univ. Sani Nassif - IBM Corp.

### FAST AND LOSSLESS GRAPH DIVISION METHOD FOR LAYOUT 2A.4S **DECOMPOSITION USING SPOR-TREE**

Wai-Shing Luk - Fudan Univ.

Huiping Huang - Cadence Design Systems, Inc.

### 2A.5S DESIGN DEPENDENT PROCESS MONITORING FOR BACK-END MANUFACTURING COST REDUCTION

Tuck-Boon Chan, Aashish Pant, Lerong Cheng, Puneet Gupta -Univ. of California, Los Angeles

2:00 - 4:00pm Pine Ballroom Cedar Ballroom 2:00 - 4:00pm

## SESSION 2B • ADVANCES IN EMBEDDED SYSTEMS AND FPGA SYNTHESIS

Swamy Muddu - GLOBALFOUNDRIES Moderator:

This session presents four papers that advance the state-of-the-art in multi-core embedded systems design and FPGA Synthesis. The first paper proposes new state space models and Monte Carlo simulation techniques to provide stochastic estimations of execution time instead of relying on worst-case estimates. The second and third paper propose new theoretical techniques for adaptive and real-time dynamic frequency and voltage scaling of embedded multi-core systems. The fourth paper proposes a new way to decompose FPGA look-up tables to improve the robustness of the FPGA logic fabric.

- 2B.1\(\beta\) SETS: STOCHASTIC EXECUTION TIME SCHEDULING FOR MULTICORE SYSTEMS BY JOINT STATE SPACE AND MONTE CARLO

- Nabeel Igbal, Jörg Henkel Karlsruhe Institute of Technology

- COMBINING OPTIMISTIC AND PESSIMISTIC DVS SCHEDULING: AN 2B.2 **ADAPTIVE SCHEME AND ANALYSIS**

Simon Perathoner - ETH Zürich Jian-Jia Chen - Karlsruhe Institute of Technology Nikolay Stoimenov, Lothar Thiele, Kai Lampka - ETH Zürich

- UNIFIED THEORY OF REAL-TIME TASK SCHEDULING AND DYNAMIC 2B.3 **VOLTAGE/FREQUENCY SCALING ON MPSOCS** Hessam Kooti, Eli Bozorgzadeh - Univ. of California, Irvine

- IN-PLACE DECOMPOSITION FOR ROBUSTNESS IN FPGA 2B.4 Ju-Yueh Lee, Zhe Feng, Lei He - Univ. of California, Los Angeles

# SESSION 2G • ENHANCING TEST FOR DELAYS AND OPENS UNDER POWER-SENSITIVE CONDITIONS

Surivaprakash Natarajan - Intel Corp. Moderator:

This session presents four papers which focus on the test of power-sensitive circuits for delays and opens. The first paper presents a method for reducing switching activity and maximizing fault coverage though intelligent partitioning of scan chains. The second paper proposes a framework for detecting stuck-open faults on power switches used in MTCMOS circuits where multiple thresholds to enable the moderation of power consumption via gating. The third paper presents an analysis of IR-drop that includes modeling the power grid. The last paper presents novel methods for selecting traced signals to determine the root cause of timing failures in the presence of power droop.

MVP: CAPTURE-POWER REDUCTION WITH MINIMUM-VIOLATIONS 2C.1 PARTITIONING FOR DELAY TESTING

Zhen Chen - Tsinahua Univ.

Krishnendu Chakrabarty - Duke Univ.

Dong Xiang - Tsinghua Univ.

2C.2 TESTING METHODS FOR DETECTING STUCK-OPEN POWER SWITCHES IN COARSE-GRAIN MTCMOS DESIGNS

> Szu-Pang Mu, Willy Wang, Hao-Yu Yang, Mango Chao - National Chiao Tuna Univ. Shi-Hao Chen, Chih-Mou Tseng, Tsung-Ying Tsai - Global Unichip Corp.

2C.3 A SCALABLE QUANTITATIVE MEASURE OF IR-DROP EFFECTS FOR SCAN PATTERN GENERATION

> Meng-Fan Wu - National Taiwan Univ. Kun-Han Tsai, Wu-Tung Cheng - Mentor Graphics Corp. Hsin-Cheih Pan, Jiun-Lang Huang, - National Taiwan Univ. Augusli Kifli - Faraday Technology Corp.

2C.4 TRACE SELECTION FOR IMPROVING TIMING AND LOGIC VISIBILITY FOR POST-SILICON VALIDATION

Hamid Shoiaei, Azadeh Davoodi - Univ. of Wisconsin

2:00 - 4:00pm

Oak Ballroom

## TUTORIAL 2 • RELIABILITY ANALYSIS AND OPTIMIZATION AT SYSTEM-LEVEL: A STRADDLE BETWEEN COMPLEXITY AND ACCURACY

Moderator: Jürgen Teich - Univ. of Erlangen-Nuremberg

Ever shrinking device structures and the rapidly growing number of system makes system level reliability analysis and optimization mandatory. A prerequisite to find a reasonable trade-off between reliability and other design objectives is an understanding of the complexity of the mathematical models typically applied at system level and, at the same time, a detailed knowledge about the physical mechanisms that cause component failures during both manufacturing and operation. This makes system level reliability analysis and optimization a multi-disciplinary task. However, reliability analysis as an enabler to introduce reliability-increasing techniques efficiently raises two important questions for the designer:

- (1) How to appropriately model and quantify the significant causes of failures at system level where significant design decisions typically made at lower levels may not be even taken?

- (2) How to handle the complexity of reliability analysis at system level where a system may be composed of hundreds or thousands of components and subsystems?

In this tutorial, we will cover the key concepts and state-of-the-art methodologies for reliability analysis and optimization at system level. A special emphasis is put on how efficient system level models that aim to cope with the complexity may interact with models to quantify the effects of physical causes of failure applied at lower levels of abstraction. We will give a bottom up survey of the state-of-the-art for a wide range of aspects including symbolic system level analysis, efficient analysis of thermal effects on reliability, design of error-resilient components, and the impact of design variability on system level reliability analysis.

## SYSTEM-LEVEL IMPACT OF CHIP-LEVEL FAILURE MECHANISMS AND **SCREENS**

Anne Gattiker - IBM Corp.

## CROSS-LAYER ERROR RESILIENCE FOR ROBUST SYSTEMS

Larkhoon Leem, Hyungmin Cho, Hsiao-Heng Lee, Young Moon Kim, Yanjing Li, Subhasish Mitra - Stanford Univ.

## RELIABILITY, THERMAL, AND POWER MODELING AND OPTIMIZATION Robert Dick - Univ. of Michigan

## SYMBOLIC SYSTEM-LEVEL RELIABILITY ANALYSIS

Michael Glass, Martin Lukasiewycz, Felix Reimann, Christian Haubelt, Jürgen Teich - Univ. of Erlangen-Nuremberg

4:30 - 6:00pm Fir Ballroom 4:30 - 6:00pm Pine Ballroom

## SESSION 3A • ADVANCED SCHEDULING FOR **MEMORY SYSTEMS**

Deming Chen - Univ. of Illinois at Urbana-Champaign Moderators: Suna Kvu Lim - Georgia Institute of Technology

This session presents scheduling works that achieve performance and power-efficient usage in various memory systems. The first paper proposes a hierarchical memory scheduling policy to minimize interferences among requests in Multimedia Multi-Processor System-on-Chip. The second paper applies so called Credit-Borrow-and-Repay technique from the networking community for multi-port DRAM sharing. The last paper presents a 3-stage ILP-based scheduling work for scratchpad memory system in embedded processors for code overlay overhead minimization.

- 3A.1 HIERARCHICAL MEMORY SCHEDULING FOR MULTIMEDIA MPSOCS Ye-Jyun Lin, Chia-Lin Yang, Jiao-Wei Huang - National Taiwan Univ. Tay-Jyi Lin - Industrial Technology Research Institute Jiao-Wei Huang - National Taiwan Univ. Naehyuck Chang - Seoul National Univ.

- 3A.2 **CREDIT BORROW AND REPAY: SHARING DRAM WITH MINIMUM** LATENCY AND BANDWIDTH GUARANTEES Zefu Dai, Mark Jarvin, Jianwen Zhu - Univ. of Toronto

- 3A.3 SCHEDULING OF SYNCHRONOUS DATA FLOW SPECIFICATIONS ON SCRATCHPAD MEMORY BASED EMBEDDED PROCESSORS Weijia Che, Karam S. Chatha - Arizona State Univ.

## SESSION 3B • MAKING CRITICAL DECISION ON **POWER IN PHYSICAL SYNTHESIS**

Moderators: Gi-Joon Nam - IBM Corp.

Lars Hagen - Cadence Design Systems, Inc.

Several novel ideas for power minimization in physical synthesis optimization will be presented in this session. The session starts with the fast and optimal peak power density minimization idea for voltage partitioning applications where an elegant binary search-based algorithm is devised. The second paper demonstrates that the significant power saving is possible even under density/timing constraints during post-placement optimization with multi-bit flip-flops. The final paper reveals interesting relationship between power optimization and fault-tolerancy in FPGA physical synthesis, showing great promise for co-optimization of power and reliability in FPGA CAD systems.

THE FAST OPTIMAL VOLTAGE PARTITIONING ALGORITHM FOR PEAK 3B.1 POWER DENSITY MINIMIZATION

Jia Wang, **Shiyan Hu** - Michigan Technological Univ.

3B.2 POST-PLACEMENT POWER OPTIMIZATION WITH MULTI-BIT FLIP-FLOPS

> Yao-Tsung Chang, Chih-Cheng Hsu, Mark Po-Hung Lin - National Chuna Chena Univ.

Yu-Wen Tsai, Sheng-Fong Chen - Faraday Technology Corp.

3B.3 ON POWER AND FAULT-TOLERANT OPTIMIZATION IN FPGA PHYSICAL SYNTHESIS

Manu Jose - Univ. of California, Los Angeles

Yu Hu - Univ. of Alberta

Rupak Majumdar - Univ. of California, Los Angeles

4:30 - 6:00pm

Cedar Ballroom

# SESSION 3C • ADVANCES IN YIELD AND QUALITY ANALYSIS

Haluk Konuk - Broadcom Corp. Moderator:

This session presents three papers which enhance analysis of yield and test quality for memories and analog circuits. The first paper presents a means of sharing redundant resources in 3-D memory architectures to maximize yield. The second paper presents a mathematical model for estimating yield--bypassing the need for expensive simulation. Finally, the third paper introduces a statistical method for estimating analog test metrics (i.e. test escapes and yield loss) for alternate tests with parts-per-million accuracy prior to production.

3C.1B YIELD ENHANCEMENT FOR 3-D-STACKED MEMORY BY REDUNDANCY **SHARING ACROSS DIES**

Li Jiang, Rong Ye, Qiang Xu - The Chinese Univ. of Hong Kong

3C.2 MATHEMATICAL YIELD ESTIMATION FOR TWO-DIMENSIONAL-**REDUNDANCY MEMORY ARRAYS**

> Mango Chao, Ching-Yu Chin, Chen-Wei Lin - National Chiao Tung Univ.

3C.3 ANALOG TEST METRICS ESTIMATES WITH PPM ACCURACY Haralampos-G. Stratigopoulos, Salvador Mir - TIMA Laboratory/CNRS

4:30 - 6:00pm

Oak Ballroom

## TUTORIAL 3 • ANALOG CHALLENGES IN NANOMETER CMOS AND DIGITALIZATION OF **ANALOG FUNCTIONALITY**

Moderator: Stephan Henzler - Infineon Technologies AG

Analog integrated circuits are a key component in many mixed-signal systems. Their design complexity, however, poses serious challenges in terms of design and verification productivity. This tutorial presents recent developments in this area.

It first reviews state-of-the-art techniques for automated design of analog circuits. Recently developed extensions towards the hierarchical design of larger building blocks and towards considering the growing variability and growing impact of time-dependent degradation phenomena such as NBTI on the performance and lifetime of analog integrated circuits will be described. Now that CMOS transistors have clearly demonstrated the ability to operate with high performance at mm-wave frequencies, there has been significant recent interest in leveraging the 60GHz band to enable multi-Gb/s wireless communications, e.g., for embedding low-cost, multi-Gb/s transceivers for file transfer and data synchronization into mobile devices such as smart-phones and digital cameras. However, realizing this scenario requires complete transceivers that dissipate roughly an order of magnitude lower power than current designs without sacrificing throughput.

The second part will discuss how to substantially improve transceiver energy-efficiency by utilizing simple modulation schemes with broadband mixed-signal circuits performing the majority of the high-speed signal processing. Mixed-signal circuit design in nanometer technologies becomes increasingly challenging due to reduced intrinsic transistor gain, diminishing voltage head-room, and variations. Digital assist techniques, however, help to circumvent these challenges. Calibration techniques or advanced system architectures such as the non-binary successive approximation ADCs are early but successful examples. The move from the voltage to the

time-domain is a recent approach to take best advantage from technology scaling, to overcome parasitic analog effects, and to enable completely new functionality.

In the third part, the reason for the push to the time domain is explained. The most important TDC applications are introduced and compared to their analog counterpart. TDC fundamentals, design challenges and latest results are discussed.

## **DESIGN AUTOMATION TOWARDS RELIABLE ANALOG** INTEGRATED CIRCUITS

Georges Gielen, Elie Maricau, Pieter De Wit - Katholieke Univ. Leuven

**ENERGY-EFFICIENT 60GHZ WIRELESS TRANSCEIVER DESIGN Elad Alon** - Univ. of California, Berkeley

DIGITALIZATION OF MIXED-SIGNAL IN NANOMETER TECHNOLOGIES

Stephan Henzler - Technische Univ. München

## Monday, November 8, 2010

# **ACM/SIGDA Member Meeting**

6:30 - 8:30pm Donner Ballroom

## 2010 SIGDA Pioneering Achievement Award Recipient

INVITED SPEAKER: Scott Kirkpatrick, The Hebrew Univ. of Jerusalem

Please join us for dinner and an entertaining talk by Scott Kirkpatrick, a pioneer in stochastic optimization.

Simulated annealing, a key element of many modern design automation tools, has its roots in the early work done by Kirkpatrick's group at IBM.

# Please join usl

# **Meetings at ICCAD**

Sunday, November 7

## The ACM/SIGDA CADathlon

7:30am – 5:00pm Donner Ballroom

Monday, November 8

## **ACM/SIGDA Member Meeting**

6:30 -8:30pm Donner Ballroom

# 48th DAC Technical Program Committee Meeting

6:30 - 8:30pm Siskiyou Ballroom Tuesday, November 9

# **48th DAC Exhibitor Meeting** 3:00pm

Carmel Room

Wednesday, November 10

## **EDAC Emerging Companies Committee**

6:30 – 10:00pm Oak Ballroom

8:30 - 10:00am Fir Ballroom

## SESSION 4A • DESIGN OPTIMIZATION FOR POWER-EFFICIENT SYNCHRONOUS AND **ASYNCHRONOUS SYSTEMS**

Moderator: Sung Kyu Lim - Georgia Institute of Technology

This session begins with two papers on low power Network-on-Chip (NOC). The first paper presents a virtual channel failure metric to capture the impact of virtual channels on the power and performance profile of NoC. The second paper proposes a Lagrangian relaxation-based simultaneous task and voltage scheduling algorithm for energy minimization in NoC. The third paper presents a methodology that characterizes aging-duty cycle and aging-supply voltage relationships to minimize power consumption and task execution time. The last paper presents a branch-and-bound-based scheduling algorithm for asynchronous systems under latency, area, energy, and power constraints.

### 4A.1 EFFICIENT TRACE-DRIVEN METAHEURISTICS FOR OPTIMIZATION OF **NETWORKS-ON-CHIP CONFIGURATIONS**

Andrew B. Kahng, Bill Lin, Kambiz Samadi, Rohit Sunkam Ramanujam - Univ. of California, San Diego

### A SELF-EVOLVING DESIGN METHODOLOGY FOR POWER EFFICIENT 4A.2 **MULTI-CORE SYSTEMS**

Jin Sun, - Univ. of Arizona Rui Zheng, Jyothi Velamala, Yu Cao - Arizona State Univ. Roman Lysecky, Karthik Shankar, Janet Roveda - Univ. of Arizona

### 4A.3S AN ENERGY AND POWER-AWARE APPROACH TO HIGH-LEVEL SYNTHESIS OF ASYNCHRONOUS SYSTEMS John Hansen, Montek Singh - Univ. of North Carolina, Chapel Hill

**CLUSTERING-BASED SIMULTANEOUS TASK AND VOLTAGE** 4A.4S SCHEDULING FOR NOC SYSTEMS

Yifang Liu - Google Inc. Yu Yang, Jiang Hu - Texas A&M Univ.

# All speakers are denoted in bold | S - denotes short paper | B - denotes best paper candidate **Tuesday, November 9, 2010**

8:30 - 10:00am Pine Ballroom 8:30 - 10:00am Cedar Ballroom

## SESSION 4B • IMPROVING SIMULATION **PERFORMANCE**

Moderators: L. Miguel Silveira - Cadence Research Labs, INESC-ID/IST - TU

Lisbon

Ting Mei - Sandia National Labs

The papers in this session address the issue of simulation performance. The first two papers consider macromodeling as a way to improve simulation efficiency and extend concepts from oscillator analysis to more general systems. The first paper extends the notion of timing/phase macromodels to general oscillatory and non-oscillatory systems. The second paper extends the notion of phase equations to quasi-periodic systems. The last paper considers runtime adaption for improving the efficiency of multialgorithm parallel simulation.

- 4B.18 GENERALIZED NONLINEAR TIMING/PHASE MACROMODELING: THEORY, NUMERICAL METHODS AND APPLICATIONS Chenije Gu, Jaijeet Roychowdhury - Univ. of California, Berkeley

- PHASE EQUATIONS FOR QUASI-PERIODIC OSCILLATORS 4B.2 Alper Demir - Koc Univ. Chenije Gu, Jaijeet Rovchowdhury - Univ. of California, Berkeley

- ON-THE-FLY RUNTIME ADAPTATION FOR EFFICIENT EXECUTION OF 4B.3 PARALLEL MULTI-ALGORITHM CIRCUIT SIMULATION Xiaoji Ye, Peng Li - Texas A&M Univ.

## SESSION 4C • ADVANCES IN GLOBAL ROUTING

Patrick Groeneveld - Magma Design Automation, Inc. Moderators: Mustafa Ozdal - Intel Corp.

This session focuses on the recent advances in global routing. In the first presentation, a novel pre-processing technique is proposed to resolve congestion hot-spots efficiently by pre-determining the detours. The second presentation focuses on the antenna avoidance problem, and shows that antenna violations can be reduced significantly when considered during global routing. The third presentation proposes an approach for global routing, where the runtime advantages of 2-D routing are maintained while 3-D layer constraints for critical nets are considered.

- 4C.1 AN AUCTION BASED PRE-PROCESSING TECHNIQUE TO DETERMINE **DETOUR IN GLOBAL ROUTING** Yue Xu, Chris Chu - Iowa State Univ.

- 4C.2 SIMULTANEOUS ANTENNA AVOIDANCE AND VIA OPTIMIZATION IN LAYER ASSIGNMENT OF MULTI-LAYER GLOBAL ROUTING Tsung-Hsien Lee, Ting-Chi Wang - National Tsing-Hua Univ.

- 4C.3 GLADE: A MODERN GLOBAL ROUTER CONSIDERING LAYER DIRECTIVES

Yen-Jung Chang, Tsung-Hsien Lee, Ting-Chi Wang - National Tsing-Hua Univ.

8:30am - 12:00pm

Oak Ballroom

## TUTORIAL 4 • SYSTEM-LEVEL DESIGN - AN INDUSTRIAL PERSPECTIVE

Moderator: Guido Stehr - Infineon Technologies AG

The term system-level design does not mean a certain methodology, but refers to a variety of design techniques well above RTL. It is a vibrant and evolving area from a methodological point of view.

This tutorial dips into the topic from a variety of angles and examines what has arrived in the industrial practice. The tutorial starts off with an introductory overview presentation on transaction level modeling.

The following five focus presentations zoom in on particular aspects touched in the first talk and elaborate on them:

The first focus presentation discusses how standardization is key for the advancement of industrial-level system design methodologies.

The next talk shows how complex on-chip communication networks can be mastered through abstraction.

The third focus presentation discusses how low-power design starts at system-level. The particular challenges of parallel system design will be explained next.

The final presentation shows how to design application specific processors, which are a compromise between general purpose cores and custom hardware.

## TRANSACTION LEVEL MODELING IN PRACTICE: MOTIVATION AND INTRODUCTION

Guido Stehr, Josef Eckmueller - Infineon Technologies AG

## STANDARDS FOR SYSTEM-LEVEL DESIGN

Laurent Maillet-Contoz - STMicroelectronics

## **DESIGN SPACE EXPLORATION AND PERFORMANCE EVALUATION AT** ELECTRONIC SYSTEM-LEVEL FOR NOC-BASED MPSOC

Soeren Sonntag, Francisco Gilabert - Lantig Deutschland GmbH

## **ESL SOLUTIONS FOR LOW POWER DESIGN**

Sylvian Kaiser, Iliia Materic, Rabih Saade - DOCEA Power SAS

## **HW/SW CO-DESIGN OF PARALLEL SYSTEMS**

Enno Wein - ProximusDA GmbH

## APPLICATION SPECIFIC PROCESSOR DESIGN

Achim Nohl, Frank Schirrmeister, Drew Taussig - Synopsys, Inc.

# All speakers are denoted in bold | S - denotes short paper | B - denotes best paper candidate **Tuesday, November 9, 2010**

Fir Ballroom Cedar Ballroom 10:30am - 12:00pm 10:30am - 12:00pm

## SESSION 5A • SYSTEM-LEVEL STATIC AND DYNAMIC **LOW POWER DESIGN**

Moderators: Karam Chatha - Arizona State Univ.

Sri Parameswaran - Univ. of New South Wales

The session includes three papers that address compiler oriented and memory access pattern based low power design approaches. The compiler oriented approaches address selective power gating of functional units in the context of reconfigurable and general purpose processors, respectively. Memory access pattern approach utilizes cache miss statistics for run time dynamic voltage frequency scaling.

## 5A.1B SELECTIVE INSTRUCTION SET MUTING FOR ENERGY-AWARE ADAPTIVE PROCESSORS

Muhammad Shafique, Lars Bauer, Jörg Henkel - Karlsruhe Institute of Technology

### 5A.2 **OPTIMAL ALGORITHM FOR PROFILE-BASED POWER GATING: A** COMPILER TECHNIQUE FOR REDUCING LEAKAGE ON EXECUTION UNITS IN MICROPROCESSORS

Danbee Park - Seoul National Univ. Nam Sung Kim, Jungseob Lee - Univ. of Wisconsin Taewhan Kim - Seoul National Univ.

### 5A.3 MEMORY ACCESS AWARE ON-LINE VOLTAGE CONTROL FOR PERFORMANCE AND ENERGY OPTIMIZATION

Xi Chen, Chi Xu - Univ. of Minnesota Robert P. Dick - Univ. of Michigan

## SESSION 5B • LEVERAGING LOGICS, WIRE AND 3-D FOR PHYSICAL SYNTHESIS

Moderators: Shiyan Hu - Michigan Technological Univ.

Gi-Joon Nam - IBM Corp.

The papers of this session address various topics related to physical synthesis. The first paper proposes a retiming-based transformation system that performs multiple optimizations simultaneously on large design partitions. The second paper proposes a post-mask ECO timing optimization flow consisting of resource-aware spare-cell selection and redundant-wireaware ECO routing. The last paper in the session discusses the impact of TSV management and develops a 3-D physical design flow that controls the number of TSVs for performance improvement.

### SPIRE: A RETIMING-BASED PHYSICAL-SYNTHESIS 5B.1 TRANSFORMATION SYSTEM

David A. Papa - IBM Corp., Univ. of Michigan Smita Krishnaswamy - IBM Corp. Igor L. Markov - Univ. of Michigan

### REDUNDANT-WIRES-AWARE ECO TIMING AND MASK-COST 5B.2 **OPTIMIZATION**

Shao-Yun Fang - National Taiwan Univ. Yao-Wen Chang, Tzuo-Fan Chien - National Taiwan Univ.

### 5B.3 THROUGH SILICON VIA MANAGEMENT DURING 3-D PHYSICAL **DESIGN: WHEN TO ADD AND HOW MANY?**

Mohit Pathak, Young-Joon Lee, Thomas Moon, Sung Kyu Lim-Georgia Institute of Technology

Pine Ballroom

10:30am - 12:00pm

DESIGNER TRACK • WRAPPING UP DESIGN SUCCESSFULLY: SIGN-OFF, VERIFICATION, DEBUG

Moderator: Andreas Herkersdorf - Technische Univ. München

This session addresses important design flow issues from a practical point of view. The first talk discusses the burning problem of an analog and mixed-signal design flow with seamless propagation of the specification through abstraction levels and tools. It analyzes today's industrial design flow and proposes practical requirements for a specification-driven flow. The second talk's topic is assertionbased verification of digital designs. Using an AHB2Wishbone bus bridge, the talk presents how a verification plan and design specifications can be completed in practice. The third talk deals with designing chips such that bug hunting in silicon is facilitated. A structured process using formal methods for handling traces and fixing bugs is presented and illustrated in practice.

- INDUSTRY NEEDS A NEW MIXED SIGNAL DESIGN AND SIGN-OFF 5D.1 SIMULATION FLOW Stephan Endrass, Matthias Arnold - Texas Instruments, Inc.

- HOW DO I KNOW I HAVE WRITTEN ENOUGH ASSERTIONS? 5D.2 Anders Nordstrom - OneSpin Solutions

- 5D.3 FORMAL METHODS APPLIED IN POST-SILICON DEBUG **Lawrence Loh** - Jasper Design Automation, Inc.

12:00 - 1:15pm

Donner/Siskiyou Ballrooms

## LUNCH PRESENTATION • SEMICONDUCTOR AND **EDA INDUSTRY - A NEW BUSINESS MODEL**

Organizer: Shishpal Rawat - Intel Corp. Speaker: Lucio Lanza - Lanza Tech Ventures

EDA industry path to revenues beyond the \$4 billion mark, where it has been stuck for its core technologies, will have to make some serious course corrections to surpass it. It is clear that to find growth again, the EDA industry needs to embrace new business models. As the cost of building ICs has ballooned the EDA industry has not done much to help new start ups reduce the cost of new design either via flexible software services or flexible manufacturing operations. New process nodes are coming on as fast as ever, but they are not ramping to use by mainstream chip designers nearly as fast due to the escalated costs. The traditional industry segments are holding on too long to their old business models. We will discuss how new business models may resurrect the chip design industry and create new focus areas for design and EDA professionals.

Sponsored by:

# All speakers are denoted in bold |S| - denotes short paper |B| - denotes best paper candidate **Tuesday, November 9, 2010**

1:30 - 3:30pm Oak Ballroom

## TUTORIAL 5 • BEYOND-DIE DESIGNS: SOLUTIONS **AND CHALLENGES**

Moderator: Yao-Wen Chang - National Taiwan Univ.

Due to the higher complexity and performance requirements in chip designs, the I/O count increases significantly, and thus more I/O signals come out of chips and run among chips, packages, and printed circuit boards (PCBs). How to complete the layout design and simultaneously satisfy various physical and electrical constraints for so many I/O signals has become a significant challenge to chip, package, and PCB designers.

This tutorial provides attendees state-of-the-art knowledge about the current industry practice and research and development for the designs of packages and PCBs and chip-package-board co-design, co-extraction, and co-simulation.

The tutorial will first describe the often overlooked design bottleneck of PCBs which are a significant cost element of the final product. This bottleneck can be greatly reduced by implementing a cross-domain codesign flow that considers the physical layout requirements of the package substrate, and the PCB in the context of planning the chip.

The tutorial will then describe the challenges that the industry encounters in moving towards a true cross-domain co-design platform, propose some possible solutions, and cover what leading companies are already doing today in the area of physical codesign. Then, recent research progress in the physical design of PCBs and packages and their codesign with chips will be treated; in particular, new models and algorithms for handling the individual- and codesign problems will be presented.

Finally, the growing electromagnetic coupling among chips, packages and PCBs, due to the ever-increasing system performance and integration density, will be described. With emphasis on power delivery network and high-speed signaling, existing solutions to estimate and model SI and PI for chip, package and PCB without completed designs are introduced, strategies to comodel and co-optimize chip, package and PCB for SI and PI are discussed, and pressing open challenges are identified.

## **BEYOND DIE DESIGN: BOARD DRIVEN I/O PLANNING & OPTIMIZATION**

John F. Park - Mentor Graphics Corp.

## RECENT RESEARCH DEVELOPMENT IN PCB LAYOUT

Tan Yan - Synopsys, Inc., Univ. of Illinois at Urbana-Champaign Martin D.F. Wong - Univ. of Illinois at Urbana-Champaign

## RECENT RESEARCH DEVELOPMENT IN FLIP-CHIP ROUTING

Hsu-Chieh Lee, Yao-Wen Chang, Po-Wei Lee - National Taiwan Univ.

## MODELING AND DESIGN FOR BEYOND-THE-DIE POWER INTEGRITY

Yivu Shi, Lei He - Univ. of California, Los Angeles

1:30 - 3:30pm Fir Ballroom 1:30 - 3:30pm Pine Ballroom

## SESSION 6A • ADVANCES IN BIOLOGICAL AND POST-**CMOS SYSTEMS**

Radu Zlatanovici - Cadence Design Systems, Inc. Moderators:

Nishant Patil - Stanford Univ.

This session presents three papers describing recent advances in biological and post-CMOS systems. The first paper presents a synthesis approach for digital signal processing operations with DNA and demonstrates the methodology on digital filters. The second paper introduces pin-count reduction algorithm for microfluidic applications based on a two-step flow formulation procedure that minimizes pin-count and wirelength. The third paper provides a comprehensive survey and modeling of sensing circuits for spin-transfer torque random access memory (STT-RAM) and propose a voltage-driven sensing scheme to improve sense margin and yield.

### A SYNTHESIS FLOW FOR DIGITAL SIGNAL PROCESSING WITH 6A.1 **BIOMOLECULAR REACTIONS**

Hua Jiang, Aleksandra Kharam, Marc Riedel, Keshab Parhi - Univ. of Minnesota

- 6A.2 A NETWORK-FLOW BASED PIN-COUNT AWARE ROUTING ALGORITHM FOR BROADCAST ELECTRODE-ADDRESSING EWOD CHIPS Tsung-Wei Huang, Shih-Yuan Yeh, Tsung-Yi Ho - National Cheng Kung Univ.

- 6A.3 VARIATION TOLERANT SENSING SCHEME OF SPIN-TRANSFER TORQUE MEMORY FOR YIELD IMPROVEMENT **Zhenyu Sun**, Hai Li - Polytechnic Institute of New York Univ. Yiran Chen, Xiaobin Wang - Seagate Technology

## SESSION 6B • PUSHING CLOCK DISTRIBUTION **PERFORMANCE**

Chris Chu - Iowa State Univ. Moderators: Dwight Hill - Synopsys, Inc.

The clocks in a chip represent its pulse, and the energy they consume comprise a major portion of its power consumption. Each picosecond of clock skew comes right off the top of critical-path timing. These four papers present new techniques for squeezing out the skew in clock networks while simultaneously minimizing power. They use the ISPD clock tree synthesis benchmarks to demonstrate effectiveness.

6B.1 **NOVEL BINARY LINEAR PROGRAMMING FOR HIGH PERFORMANCE CLOCK MESH SYNTHESIS**

Minsik Cho - IBM Corp. David Z. Pan - Univ. of Texas. Austin Ruchir Puri - IBM Corp.

6B.2 LOW-POWER CLOCK TREES FOR CPUS

Dong-Jin Lee, Myung-Chul Kim, Igor L. Markov - Univ. of Michigan

6B.3 HIGH VARIATION-TOLERANT OBSTACLE-AVOIDING CLOCK MESH SYNTHESIS WITH SYMMETRICAL DRIVING TREES

Xin-Wei Shih, Hsu-Chieh Lee, Kuan-Hsien Ho, Yao-Wen Chang -National Taiwan Univ.

6B.4 LOCAL CLOCK SKEW MINIMIZATION USING BLOCKAGE-AWARE MIXED TREE-MESH CLOCK NETWORK

> Linfu Xiao, Zigang Xiao, Zaichen Qian, Yan Jiang, Tao Huang, Haitong Tian, Evangeline F.Y. Young - The Chinese Univ. of Hong Kong

# All speakers are denoted in bold |S| - denotes short paper |B| - denotes best paper candidate **Tuesday, November 9, 2010**

1:30 - 3:30pm

Cedar Ballroom

## SESSION 6C • 3-D-ICS AND DETECTION OF FAULTS AND HARDWARE TROJANS

Moderators: Jinfeng Liu - Synopsys, Inc.

Zhenyu Qi - Broadcom Corp.

This session presents three papers on 3-D-ICs, a paper on the detection of faults and another on the detection of Hardware Trojans (HTs). The first paper on 3-D-ICs focuses on thermal modeling of 3-D-ICs cooled using microfluidic chanels, the second focuses on the test cost for 3-D-ICs, and the third one considers alternatives to Through-Silicon Vias (TSVs) by using inductive or capacitive coupling solutions.

### 6C.1 3-D-ICE: FAST COMPACT TRANSIENT THERMAL MODELING FOR3-D ICS WITH INTER-TIER LIQUID COOLING

Arvind Sridhar, Alessandro Vincenzi, Martino Ruggiero, - Ecole Polytechnique Fédérale de Lausanne Thomas Brunschwiler - IBM Corp.

David Atienza - Ecole Polytechnique Fédérale de Lausanne

### **COST-EFFECTIVE INTEGRATION OF THREE-DIMENSIONAL (3-D) ICS** 6C.2 **EMPHASIZING TESTING COST ANALYSIS**

Yibo Chen, Dimin Niu, Yuan Xie - Pennsylvania State Univ. Krishnendu Chakarabarty - Duke Univ.

- 6C.3S **EVALUATION OF USING INDUCTIVE/CAPACITIVE-COUPLING VERTICAL INTERCONNECTS IN 3-D NETWORK-ON-CHIP** Jin Ouyang, Jing Xie, Matthew Poremba, Yuan Xie - Pennsylvania State Univ.

- 6C.4 SCALABLE SEGMENTATION-BASED MALICIOUS CIRCUITRY **DETECTION AND DIAGNOSIS** Sheng Wei, Miodrag Potkonjak - Univ. of California, Los Angeles

- APPLICATION-AWARE DIAGNOSIS OF RUNTIME HARDWARE FAULTS 6C.5S **Andrea Pellegrini**, Valeria Bertacco - Univ. of Michigan

4:00 - 6:00pm Oak Ballroom 4:00 - 6:00pm Fir Ballroom

## TUTORIAL 6 • ORGANIC ELECTRONICS

Hagen Klauk - Max Planck Institute for Solid State Research Moderator:

Electronic devices based on conjugated organic semiconductors hold great promise for emerging applications in flexible and printed electronics. In this tutorial we will provide an overview of:

- Materials and manufacturing of organic transistors

- Design and manufacturing of organic RFID circuits

- Design of sensor and memory arrays with organic transistors

- Design of analog circuits with organic transistors

MATERIALS AND MANUFACTURING OF ORGANIC TRANSISTORS Hagen Klauk, Ute Zschieschang - Max Planck Institute for Solid State Research

**DESIGN AND MANUFACTURING OF ORGANIC RFID CIRCUITS** Jan Genoe, Kris Myny, Soeren Steudel, Paul Heremans - IMEC

## DESIGN OF LARGE AREA ELECTRONICS WITH ORGANIC TRANSISTORS

Makoto Takamiya, Koichi Ishida, Tsuyoshi Sekitani, Takao Someya, Takayasu Sakurai - The Univ. of Tokyo

## **DESIGN OF ANALOG CIRCUITS USING ORGANIC** FIELD-EFFECT TRANSISTORS

Boris Murmann, Wei Xiong - Stanford Univ.

## SESSION 7/A • ADVANCES IN TIMING ANALYSIS

Moderators: Igor Keller - Cadence Design Systems, Inc. Yaping Zhan - Advanced Micro Devices, Inc.

This session presents several recent advances in timing analysis and their applications. The first paper proposes an active learning scheme for low-cost adaptive testing based on timing modeling. The second paper develops a new tool of ternary decision diagram to analyze circuit dynamic behavior. The third paper discusses modeling and analysis techniques for latchcontrolled circuits. The final paper focuses on timing-independent false path identification.

7A.1 ACTIVE LEARNING FRAMEWORK FOR POST-SILICON VARIATION EXTRACTION AND TEST COST REDUCTION

Cheng Zhuo - Univ. of Michigan Kanak Agarwal - IBM Corp. David Blaauw, Dennis Sylvester - Univ. of Michigan

- 7A.2 ANALYSIS OF CIRCUIT DYNAMIC BEHAVIOR WITH TIMED TERNARY **DECISION DIAGRAM** Lu Wan, Deming Chen - Univ. of Illinois at Urbana-Champaign

- 7A.3 FAST STATISTICAL TIMING ANALYSIS OF LATCH-CONTROLLED CIRCUITS FOR ARBITRARY CLOCK PERIODS Bing Li, Ning Chen, Ulf Schlichtmann - Technische Univ. München

- 7A.4 ON TIMING-INDEPENDENT FALSE PATH IDENTIFICATION Feng Yuan, Qiang Xu - The Chinese Univ. of Hong Kong

4:00 - 5:30pm Pine Ballroom 4:00 - 5:30pm Cedar Ballroom

## SESSION 7B • PARALLEL METHODS FOR POWER **GRID AND INTERCONNECT ANALYSIS**

Eric Keiter - Sandia National Labs Moderators: Heidi Thornquist - Sandia National Labs

This session presents three papers on exploiting multi-core/threads for interconnect and power grid analysis. The first paper presents a technique for parameterized model-order reduction. The second paper presents a hierarchical matrix inversion algorithm for power grid analysis and the last paper presents an analysis method for the thermals in 3-D ICs.

- 3POR PARALLEL PROJECTION BASED PARAMETERIZED ORDER REDUCTION FOR MULTI-DIMENSIONAL LINEAR MODELS Jorge Fernández Villena - INESC-ID/IST - TU Lisbon L. Miguel Silveira - Cadence Research Labs, INESC-ID/IST - TU Lisbon

- 7B.2S A HIERARCHICAL MATRIX INVERSION ALGORITHM FOR VECTORLESS POWER GRID VERIFICATION Xuanxing Xiong, Jia Wang - Illinois Institute of Technology

- 7B.3S FAST THERMAL ANALYSIS ON GPU FOR 3-D-ICS WITH INTEGRATED MICROCHANNEL COOLING Zhuo Feng - Michigan Technological Univ. Peng Li - Texas A&M Univ.

## SESSION 7C • PHYSICAL DESIGN FOR **MANUFACTURABILITY AND VARIABILITY**

Yufeng Luo - Mentor Graphics Corp. Moderators: Yongseok Cheon - Synopsys, Inc.

With aggressive technology scaling that creates complicated design with staggering complexity, manufacturability and variability are important factors that cannot be ignored any futher in physical optimization. The papers in this session address manufacturability and variability at different levels and applications: wire perturbation optimization for double patterning technology, statistical design techniques and discrete gate-sizing for timing yield optimization. The first paper presents a wire perturbation algorithm to fix as many native conflicts as possible in the double patterning technology. The second paper presents a lower bound computation technique to evaluate statistical design optimization methods. The last one demonstrates that significant timing yield improvement via globallyinformed discrete gate-sizing algorithm.

- NATIVE-CONFLICT-AWARE WIRE PERTURBATION FOR DOUBLE PATTERNING TECHNOLOGY Szu-Yu Chen, Yao-Wen Chang - National Taiwan Univ.

- 7C.2 A LOWER BOUND COMPUTATION METHOD FOR EVALUATION OF STATISTICAL DESIGN TECHNIQUES Vineeth Veeti, Dennis Sylvester, David Blaauw - Univ. of Michigan

- 7C.3 TIMING YIELD OPTIMIZATION VIA DISCRETE GATE-SIZING USING GLOBALLY-INFORMED DELAY PDFS Shantanu Dutt, Huan Ren - Univ. of Illinois

# All speakers are denoted in bold | S - denotes short paper | B - denotes best paper candidate **Wednesday, November 10, 2010**

8:30am - 12:30pm

Oak Ballroom

## TUTORIAL 7 • DIGITAL MICROFLUIDIC BIOCHIPS: A VISION FOR FUNCTIONAL DIVERSITY AND MORE **THAN MOORE**

Krishnendu Chakrabarty - Duke Univ. Moderator:

Advances in droplet-based "digital" microfluidics have led to the emergence of biochip devices for automating laboratory procedures in biochemistry and molecular biology. These devices enable the precise control of nanoliter-volume droplets of biochemical samples and reagents. Therefore, integrated circuit (IC) technology can be used to transport and transport "chemical payload" in the form of micro/nanofluidic droplets. As a result, non-traditional biomedical applications and markets (e.g., high-throughout DNA sequencing, portable and point-of-care clinical diagnostics, protein crystallization for drug discovery), and fundamentally new uses are opening up for ICs and systems. However, continued growth (and larger revenues resulting from technology adoption by pharmaceutical and healthcare companies) depends on advances in chip integration and designautomation tools. In particular, design-automation tools are needed to ensure that biochips are as versatile as the macro-labs that they are intended to replace. This is therefore an opportune time for the semiconductor industry and circuit/system designers to make an impact in this emerging field.

This tutorial offers attendees an opportunity to bridge the semiconductor ICs/systems industry with the biomedical and pharmaceutical industries.

The tutorial will first describe emerging applications (market drivers) in biology and biochemistry that can benefit from advances in electronic "biochips". The presenter will next describe technology platforms for accomplishing "biochemistry on a chip", and introduce the audience to microarrays and fluidic actuation methods based on microfluidics. The droplet-based "digital" microfluidic platform based on electrowetting will be described in considerable detail.

Next, the presenter will describe fabrication techniques for digital microfluidic biochips, followed by computer-aided design, design-fortestability, and reconfiguration aspects of chip/system design. The physics of droplet flow, and advances ion modeling and simulation techniques will be covered. Synthesis algorithms and methods will be presented to map behavioral descriptions to a digital microfluidic platform, and generate an optimized schedule of bioassay operations, chip layout, and dropletflow paths. In this way, the audience will see how a "biochip compiler" can translate protocol descriptions provided by an end user (e.g., a chemist or a nurse at a doctor's clinic) to a set of optimized and executable fluidic instructions that will run on the underlying digital microfluidic platform. Testing techniques will be described to detect faults after manufacture and during field operation. A number of case studies based on representative assays and laboratory procedures will be interspersed in appropriate places throughout the tutorial.

The tutorial presenters envision an automated design flow for biochips, in the same way as design automation revolutionized IC design in the 80s and 90s. Biochip users (e.g., chemists, nurses, doctors and clinicians) and the biotech/pharmaceutical industry will adapt more easily to new technology if appropriate design tools and in-system automation methods are made available.

## DIGITAL MICROFLUIDIC BIOCHIPS: A VISION FOR FUNCTIONAL **DIVERSITY AND MORE THAN MOORE**

**Tsung-Yi Ho** - National Cheng Kung Univ. Jun Zeng - Hewlett-Packard Labs Krishnendu Chakrabarty - Duke Univ.

# All speakers are denoted in bold |S| - denotes short paper |B| - denotes best paper candidate **Wednesday, November 10, 2010**

8:30 - 10:00am Fir Ballroom Pine Ballroom 8:30 - 10:00am

## SESSION 3A • ADVANCES IN CORE LOGIC SYNTHESIS